# Kashif Javed

Model-Driven Development and Verification of Fault Tolerant Systems

TURKU CENTRE for COMPUTER SCIENCE

TUCS Dissertations No 223, May 2017

## Model-Driven Development and Verification of Fault-Tolerant Systems

Kashif Javed

To be presented, with the permission of the Faculty of Science and Engineering of the Åbo Akademi University, for public criticism in Auditorium XX on May 24<sup>th</sup>, 2017, at 12 noon.

> Turku Centre for Computer Science Åbo Akademi University Faculty of Science and Engineering Agora, Universitetsbacken, 20520 Åbo Finland

> > 2017

## Supervised by

Docent Elena Troubitsyna Faculty of Science and Engineering Åbo Akademi University Vattenborgsvägen 5, 20500 Turku Finland

## Reviewed by

Professor Anatoliy Gorbenko Department of Computer Systems and Networks National Aerospace University (KhAI) Kharkov, Ukraine

Professor Amund Skavhaug Faculty of Engineering Science and Technology Norwegian University of Science and Technology (NTNU) Trondheim, Norway

## Opponent

Professor Anatoliy Gorbenko Department of Computer Systems and Networks National Aerospace University (KhAI) Kharkov, Ukraine

ISBN 978-952-12-3553-5 ISSN 1239-1883

# Dedicated to my dearest parents who have supported me throughout my education

"Seek knowledge from the cradle to the grave." Prophet Muhammad (Peace be upon him)

## Abstract

Dependability is an ability of a computer-based system to deliver services that can be justifiably trusted. There is a wide range of computer-based systems that provide services that are critical for our society, e.g., nuclear power plants, transportation, healthcare, etc. Ensuring dependability of such systems constitutes an important engineering goal.

Dependability is an integrated notion that encompasses various system characteristics including reliability, safety, availability, etc. For a wide class of systems, the main engineering goal is to ensure a high degree of reliability – a probability of a system functioning correctly over a given period under a given set of operating conditions. Since the occurrence of faults can disrupt correct system behavior, to achieve the required reliability, we need to employ fault tolerance techniques.

The main goal of fault tolerance is to ensure that the system can deliver its services despite the occurrence of faults. Fault tolerance typically introduces some form of architectural or computational redundancy and hence, increases the complexity of the system design. Therefore, to ensure a correct implementation of fault tolerance mechanisms, we should develop the techniques that facilitate a structured analysis of system failure modes, systematic design of error recovery and reconfiguration procedures, as well as bolster system verification and validation.

Model-driven engineering allows the designers to cope with system complexity and analyze system behavior at different levels of abstraction. In our thesis, we aim at studying how to represent various static and dynamic aspects of fault tolerance in the model-driven development.

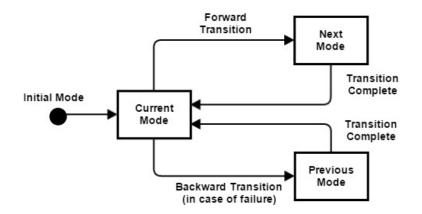

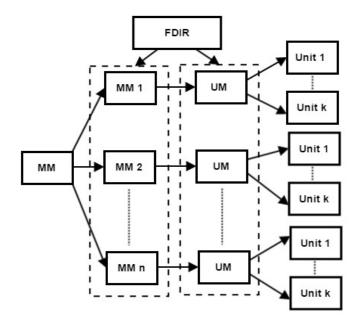

Often behavior of complex fault-tolerant systems is structured using the notion of operational modes – mutually exclusive sets of the system behavior. As a reaction on faults as well as different internal and external conditions, the system switches between its operational modes. The design of mode transition logic in distributed fault tolerant systems is a challenging and error-prone task. On the one hand, we need to ensure that all components of the system are put in the states required by a certain mode. On the other hand, we should verify that the components maintain these states while the system is stable, i.e., before the conditions for triggering a transition to another mode are reached. To facilitate the design of complex mode-rich fault tolerant systems, in our thesis, we demonstrate how to model distributed systems with centralized and distributed mode management as well as verify their mode transition logic. We validate the proposed approach in the aerospace domain.

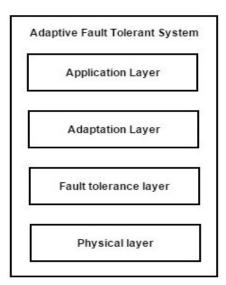

To guarantee that the reconfiguration performed in response to the changed operating conditions achieves the required goal, fault-tolerant systems should incorporate the appropriate monitoring capabilities and rely on a set of explicitly defined rules for triggering adaptation. Usually, these rules establish a connection between globally observed system properties and behavior of system components, i.e., span over several architectural layers. To facilitate the development of such complex systems, in our work, we propose the generic patterns for architecting adaptive fault tolerant systems in a layered hierarchical manner. We demonstrate how the proposed patterns can be utilized in the context of data intensive fault tolerant systems.

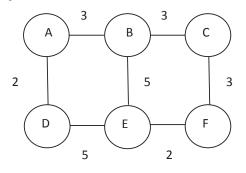

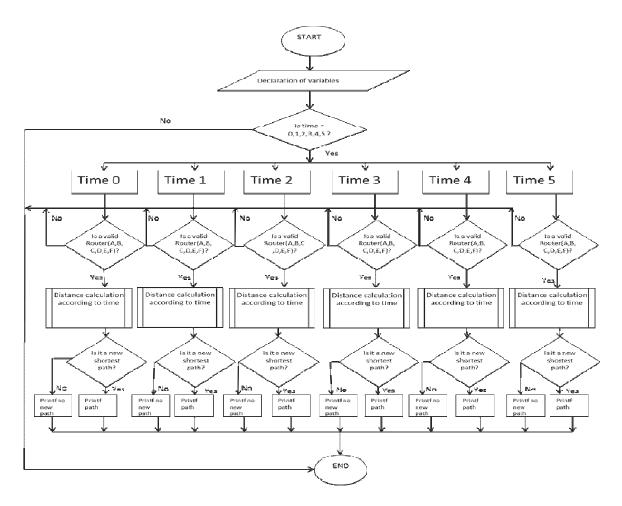

Development and verification of fault-tolerant distributed systems also require the use of advanced verification technologies as well as techniques for supporting a disciplined systematic analysis of system failure modes. In our thesis, we demonstrate how to perform formal verification of a fault tolerant routing protocol and systematically identify system failure modes and recovery procedures using Failure Modes and Effect Analysis approach. While reliance on formal techniques increases confidence in the correctness of the implementation of the fault tolerance mechanisms, the use of a systematic inductive technique for identifying failure modes improves the completeness of the analysis.

The research work performed in our thesis aims at creating a support for explicit integration of fault tolerance consideration into the model-driven system development. We aim at creating a potentially industry-relevant approach and hence, utilize the modeling and verification techniques that are used in current industrial practice. Moreover, we validate our approach in a number of case studies from different domains.

## Sammanfattning

Tillförlitlighet är ett datorbaserat systems förmåga att kunna leverera tjänster som med goda argument är pålitliga. Det finns ett brett spektrum av datorbaserade system som tillhandahåller tjänster som är avgörande för vårt samhälle, t.ex. kärnkraftverk, transport, hälso- och sjukvård osv. Att säkerställa pålitligheten för sådana system är ett viktigt tekniskt mål.

Tillförlitlighet är ett integrerat begrepp som omfattar olika systemegenskaper, inklusive funktionssäkerhet, säkerhet, tillgänglighet etc. För en omfattande klass av system är det huvudsakliga tekniska målet att säkerställa en hög grad av tillförlitlighet - en sannolikhet för att ett system fungerar korrekt under en viss period med en given mängd driftsförhållanden. Eftersom fel som uppstår kan störa ett korrekt systembeteende, måste vi använda feltoleranstekniker för att uppnå den tillförlitlighet som krävs.

Huvudmålet med feltolerans är att säkerställa att systemet kan leverera sina tjänster trots att fel uppstått. Feltolerans introducerar typiskt någon form av arkitektonisk eller beräkningsmässig redundans och ökar därigenom systemdesignens komplexitet. För att säkerställa ett korrekt genomförande av feltoleransmekanismer bör vi utveckla de tekniker som underlättar en strukturerad analys av systemfelslägen, systematisk utformning av felhantering och procedurer för omkonfiguration, samt förstärkning av systemets verifiering och validering.

Modelldriven teknik möjliggör hantering av systemkomplexitet och analys av systembeteendet på olika abstraktionsnivåer. Avhandling strävar efter att studera hur man representerar olika statiska och dynamiska aspekter av feltolerans i modelldriven utveckling.

Ofta är beteendet hos komplexa feltoleranta system strukturerat enligt operativa lägen - ömsesidigt uteslutande uppsättningar av systembeteendet. Som en reaktion på fel såväl som olika interna och externa förhållanden växlar systemet mellan sina driftlägen. Utformningen av logik för lägesövergång i distribuerade feltoleranta system är en utmanande och felbenägen uppgift. Å ena sidan måste vi se till att alla komponenter i systemet sätts i de tillstånd som krävs av ett visst läge. Å andra sidan bör vi verifiera att komponenterna upprätthåller dessa tillstånd medan systemet är stabilt, dvs. innan förutsättningarna för en övergång till ett annat läge uppnås. För att underlätta utformningen av komplexa feltoleranta system med många tillstånd, visar vi i vår avhandling hur man modellerar distribuerade system med centraliserad och distribuerad lägeshantering samt verifierar deras logik för lägesövergång. Vi validerar det föreslagna tillvägagångssättet inom rymdindustrin.

För att säkerställa att omkonfigurationen som utförts som svar på de ändrade driftsförhållandena uppnår det önskade målet, bör feltoleranta system inkludera lämplig övervakningsförmåga och förlita sig på en uppsättning uttryckligen definierade regler för start av anpassning. Vanligtvis etablerar dessa regler en koppling mellan globalt observerade systemegenskaper och beteenden hos systemkomponenter, dvs. de spänner över flera arkitektoniska skikt. För att underlätta utvecklingen av sådana komplexa system, föreslår vi i vårt arbete generiska mönster för konstruktion av adaptiva feltoleranta system på ett hierarkiskt sätt. Vi visar hur de föreslagna mönstren kan utnyttjas i samband med dataintensiva feltoleranta system.

Utveckling och verifiering av feltoleranta distribuerade system kräver också användning av avancerad verifieringsteknik samt tekniker för att stödja en systematisk analys av systemets fellägen. I vår avhandling visar vi hur man utför formell verifiering av ett feltolerant ruttningsprotokoll och systematiskt identifierar systemets fellägen och återställningsförfaranden med hjälp av FMEA (Failure Modes and Effect Analysis). Medan formella tekniker ökar konfidensen för korrekt implementering av feltoleransmekanismerna, förbättrar användningen av en systematisk induktiv teknik för identifiering av fellägen analysens fullständighet.

Forskningsarbetet i avhandlingen strävar efter att skapa stöd för en explicit integration av feltolerans i modelldriven systemutveckling. Vi strävar efter att skapa ett tillvägagångssätt som är relevant inom industrin och därför utnyttjar vi de modellerings- och verifieringsmetoder som används i nuvarande industripraxis. Dessutom validerar vi vårt tillvägagångssätt i ett antal fallstudier från olika domäner.

## Acknowledgements

First of all, I thank Almighty Allah for giving me the courage and strength to pursue my PhD research work at Åbo Akademi University, Turku, Finland. This thesis would not have been possible without the financial support of National University of Sciences and Technology, Islamabad, Pakistan.

I would like to express my gratitude to my supervisor, Associate Professor Elena Troubitsyna, for her professional guidance, full-time supervision, close monitoring and timely feedback, which has enabled me to complete this thesis. I wholeheartedly appreciate her continued support, great encouragement, valuable advice, and friendly atmosphere during the whole PhD research work. I am indebted to her for ensuring the provision of conducive and productive research environment in the Distributed Systems Laboratory of the Department of Information Technology and Turku Centre for Computer Science (TUCS). I am very grateful to the administrative and technical staff of the department and TUCS for providing full assistance during my research work.

I would like to thank my reviewers, Professor Anatoliy Gorbenko from National Aerospace University and Professor Amund Skavhaug from Norwegian University of Science and Technology, for sparing their valuable time to read the thesis and giving extremely useful suggestions for further refining and enhancing the quality of the thesis work. I am very thankful to Professor Anatoliy Gorbenko for accepting to be the opponent in the public defense of my thesis. I owe my special thanks to Professor Anatoliy Gorbenko for his precious time and efforts to act as a proof reader of my thesis. I would also like to thank Johan and Jonathan for translating the abstract of the thesis into Swedish.

I would like to extend my special appreciation to Christel Engblom who always helped me to conduct the experimental work by making necessary arrangements in the laboratory. I am grateful to Magnus Dahlvik for providing requisite computer support. I would also like to thank from the core of my heart Hans Bang Stiftelsen, Ulla Tuominen and Åbo Akademi University for awarding me the research grants during my PhD work.

I enjoyed the study and research environment provided by the Department of Information Technology and TUCS. I would like to express my special thanks to my colleagues, working in the Distributed Systems Laboratory and ICT building, for giving me technical support and providing cooperation during the tough hours of research work.

I am very grateful to my parents, Professor Muhammad Younus Javed and Manzoor Akhtar, whose prayers and patronage have played a pivotal role in the completion of this work. I would also like to extend my sincere appreciation to Dr. Qaisar Javed, Shumaila Younus and Munazza Younus who have always been a great source of inspiration and encouragement for me.

Last but not the least; I owe countless thanks to my wife, Asifa Kashif, and my son, Muhammad Umer Javed, for standing beside me throughout this

research journey. Their lovely attitude, persistent support, thorough understanding, humorous behavior and sincere prayers have greatly helped me to complete this thesis within the scheduled timeline.

Åbo, May 2017 Kashif Javed

## **List of Original Publications**

- I Kashif Javed, Asifa Kashif, and Elena Troubitsyna. Implementation of SPIN Model Checker for Formal Verification of Distance Vector Routing Protocol. In *International Journal of Computer Science and Information Security* (IJCSIS), Vol 8, No 3, pp. 1-6, ISSN 1947-5500, June 2010, USA.

- II Kashif Javed, Elena Troubitsyna. Designing a Fault-Tolerant Satellite System in SystemC. In *Proceedings of the Seventh International Conference on Systems (ICONS 2012)*, pp. 49–54, IEEE Computer Press, March 2012, Saint Gilles, Reunion Island.

- III Kashif Javed and Elena Troubitsyna. Modelling a Fault-Tolerant Distributed Satellite System. In Proceeding of the International Conference Advanced Collaborative Networks, Systems and Applications (COLLA 2012), pp. 35-41, June 2012, Venice, Italy.

- IV Kashif Javed and E. Troubitsyna, A Case Study in Modelling a Fault-Tolerant Satellite System Implementing Dynamic Reconfiguration via Handshake. In Proceedings of the Seventh International Conference on Software Engineering Advances (ICSEA2012), pp. 44-49, November 2012, Lisbon, Portugal.

- V Elena Troubitsyna and Kashif Javed. Towards Systematic Design of Adaptive Fault-Tolerant Systems. In *Proceedings of the Sixth International Conference on Adaptive and Self-Adaptive Systems and Applications (ADAPTIVE 2014)*, pp. 15-21, May 2014, Venice, Italy.

- VI Elena Troubitsyna and Kashif Javed. A Structured Approach to Architecting Fault-Tolerant Services. In *Proceedings of the Ninth International Conference on Internet and Web Applications and Services (ICIW 2014)*, pp. 99-104, July 2014, Paris, France.

## Contents

| Research Summary      |                                                                      |    |

|-----------------------|----------------------------------------------------------------------|----|

|                       | ivation and Research Objectives                                      |    |

| 2 Dep                 | endability and Fault Tolerance                                       |    |

| 2.1                   | Dependability Taxonomy                                               |    |

| 2.2                   | Fault Tolerance                                                      |    |

| 3 Desi                | ign and Verification Methods                                         |    |

| 3.1                   | UML                                                                  |    |

| 3.2                   | SystemC                                                              |    |

| 3.3                   | Model Checking Fault-Tolerant Systems                                | 27 |

| 3.3.1                 | Model Checking: Introductory Background                              |    |

| 3.3.2                 | SPIN PROMELA                                                         | 30 |

| 4 Faul                | t Tolerance in Mode-Rich System                                      | 35 |

| 4.1                   | Modes                                                                |    |

| 4.2                   | Mode-Rich Fault-Tolerant Systems: Centralized Mode Management        |    |

| 4.3                   | Mode-Rich Fault-Tolerant Systems: Distributed Mode Management        |    |

| 5 Faul                | t Tolerance in Service-Oriented Distributed Systems                  |    |

| 5.1                   | Fault Tolerance in Service Oriented Architectures                    | 51 |

| 5.2                   | Adaptive Fault-Tolerant Systems                                      | 55 |

|                       | mary of the Original Publications                                    |    |

| 7 Rela                | ted Work                                                             |    |

| 7.1                   | Modes and Fault Tolerance                                            | 65 |

| 7.2                   | Model-Driven Engineering and Verification of Fault-Tolerant Systems. | 67 |

| 7.3                   | Centralized Mode Management in Fault-Tolerant systems                | 68 |

| 7.4                   | Fault Tolerance in Distributed Systems                               |    |

| 8 Con                 | clusion and Future Work                                              | 73 |

| 8.1                   | Conclusions                                                          | 73 |

| 8.2                   | Future Work                                                          |    |

| Original Publications |                                                                      |    |

## List of Figures

| Figure 2.2: Fault Tolerance Techniques                                                                                                                                                                                                                                                                                                                                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2.4: Dynamic redundancy: standby spare15Figure 2.5: Dynamic redundancy: duplication pattern15Figure 3.1: Example of a Use Case Diagram18Figure 3.2: Example of a Class Diagram19Figure 3.3: Example of a Sequence Diagram20Figure 3.4: Examples of State Diagram (a) with explicit representation of failure10(b) with explicit representation of failure and error recovery21 |

| Figure 2.5: Dynamic redundancy: duplication pattern                                                                                                                                                                                                                                                                                                                                   |

| Figure 3.1: Example of a Use Case Diagram       18         Figure 3.2: Example of a Class Diagram       19         Figure 3.3: Example of a Sequence Diagram       20         Figure 3.4: Examples of State Diagram (a) with explicit representation of failure       (b) with explicit representation of failure and error recovery                                                  |

| Figure 3.2: Example of a Class Diagram19Figure 3.3: Example of a Sequence Diagram20Figure 3.4: Examples of State Diagram (a) with explicit representation of failure(b) with explicit representation of failure and error recovery21                                                                                                                                                  |

| Figure 3.3: Example of a Sequence Diagram                                                                                                                                                                                                                                                                                                                                             |

| Figure 3.4: Examples of State Diagram (a) with explicit representation of failure (b) with explicit representation of failure and error recovery                                                                                                                                                                                                                                      |

| Figure 3.4: Examples of State Diagram (a) with explicit representation of failure (b) with explicit representation of failure and error recovery                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                       |

| Figure 3.5: Definition of simple SystemC module                                                                                                                                                                                                                                                                                                                                       |

| Figure 3.6: SystemC template for creating ports                                                                                                                                                                                                                                                                                                                                       |

| Figure 3.7: Example of a module with a method process declaration                                                                                                                                                                                                                                                                                                                     |

| Figure 3.8: SystemC Implementation of Fault Tolerant Service Pattern                                                                                                                                                                                                                                                                                                                  |

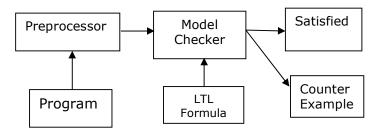

| Figure 3.9: Model Checking Process                                                                                                                                                                                                                                                                                                                                                    |

| Figure 3.10: Promela Implementation of Fault-Tolerant Service                                                                                                                                                                                                                                                                                                                         |

| Figure 3.11: Example of SPIN output                                                                                                                                                                                                                                                                                                                                                   |

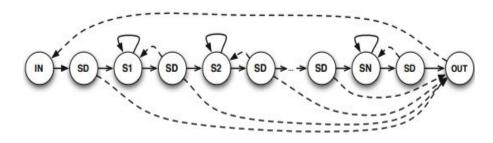

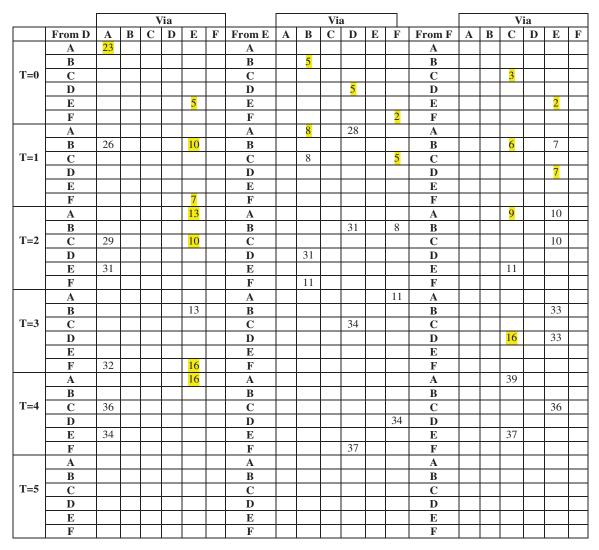

| Figure 4.1: Mode Logic of Fault-Tolerant System: a General Principle                                                                                                                                                                                                                                                                                                                  |

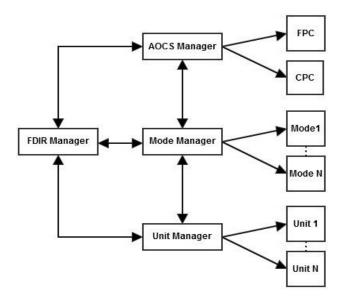

| Figure 4.2: Generic Architecture of Mode Rich Systems                                                                                                                                                                                                                                                                                                                                 |

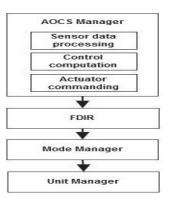

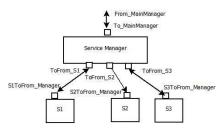

| Figure 4.3: Centralized AOCS Architecture                                                                                                                                                                                                                                                                                                                                             |

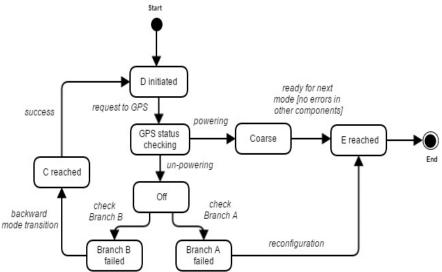

| Figure 4.4: Centralized Mode-Rich Fault-Tolerant System: Example of GPS unit                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                       |

| Figure 4.5: A general pattern for defining Mode Transition in SystemC (GPS                                                                                                                                                                                                                                                                                                            |

| instance)                                                                                                                                                                                                                                                                                                                                                                             |

| Figure 4.6: Example of Mode Transition Verification                                                                                                                                                                                                                                                                                                                                   |

| Figure 4.7: State Diagram of D-AOCS (GPS example)                                                                                                                                                                                                                                                                                                                                     |

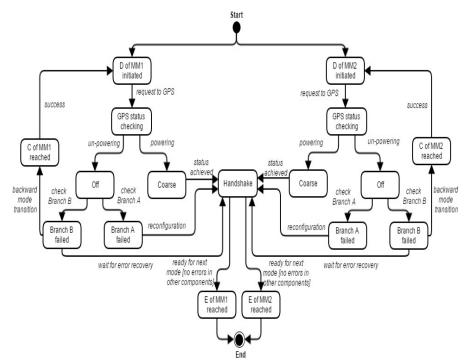

| Figure 4.8: Distributed Mode Management (GPS example)                                                                                                                                                                                                                                                                                                                                 |

| Figure 4.9: Distributed Mode Management: Verification of Handshake                                                                                                                                                                                                                                                                                                                    |

| Procedure (Mode D example)                                                                                                                                                                                                                                                                                                                                                            |

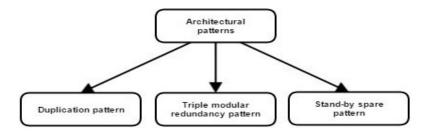

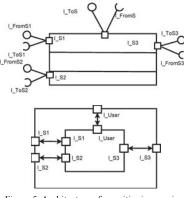

| Figure 5.1: Architectural Patterns for Introducing Redundancy                                                                                                                                                                                                                                                                                                                         |

| Figure 5.2: Service Execution Flow                                                                                                                                                                                                                                                                                                                                                    |

| Figure 5.3: Generic Form of FMEA Table                                                                                                                                                                                                                                                                                                                                                |

| Figure 5.4: Example of Failure Analysis using FMEA                                                                                                                                                                                                                                                                                                                                    |

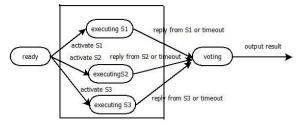

| Figure 5.5: Architecture of an Adaptive Fault-Tolerant System                                                                                                                                                                                                                                                                                                                         |

| Figure 5.6: Transitions between Adaptation Modes                                                                                                                                                                                                                                                                                                                                      |

Part I

# **Research Summary**

## 1 Motivation and Research Objectives

Dependability is an ability of a computer-based system to deliver services that can be justifiably trusted. There is a wide range of computer-based systems that provide services that are critical for our society, e.g., nuclear power plants, transportation, healthcare, etc. Ensuring dependability of such systems constitutes an important engineering goal.

Dependability is an integrated notion that encompasses various system characteristics including reliability, safety, availability, etc. For a wide class of systems, the main engineering goal is to ensure a high degree of reliability – a probability of a system functioning correctly over a given period under a given set of operating conditions. Since the occurrence of faults can disrupt correct system behavior, to achieve the required reliability, we need to employ fault tolerance techniques.

The main goal of fault tolerance is to ensure that the system can deliver its services despite the occurrence of faults. Fault tolerance typically introduces some form of architectural or computational redundancy and hence, increases the complexity of the system design. Therefore, to ensure a correct implementation of fault tolerance mechanisms, we should develop the techniques that facilitate a structured analysis of system failure modes, systematic design of error recovery and reconfiguration procedures, as well as bolster verification and validation of complex fault-tolerant systems.

This goal can be achieved by employing a model-driven development approach. Reliance on abstraction and rigorous mathematical analysis provides us with a powerful support while designing complex fault tolerant systems. However, despite the popularity of model-driven engineering, there is still a lack of approaches supporting an *explicit* modeling of fault tolerance aspects of system behavior. Our first research question

*Research question 1. How can we explicitly represent fault tolerance in the model-driven system development?*

aims at addressing this issue.

Often the behavior of complex fault-tolerant systems is structured using the notion of operational modes – mutually exclusive sets of the system behavior. As a reaction on faults as well as different internal and external conditions, the system switches between its operational modes. The design of mode transition logic in distributed fault tolerant systems is a challenging and error-prone task. On the one hand, we need to ensure that all components of the system are put in the states required by a certain mode. On the other hand, we should verify that the components maintain these states while the system is stable, i.e., before the conditions for triggering a transition to another mode are reached.

To address this challenge, we formulate the second research question:

Research question 2: How can we facilitate design and verification of complex mode-rich fault tolerant systems with centralized and distributed mode management?

Development and verification of fault-tolerant distributed systems also require the use of advanced verification technologies as well as techniques for supporting a disciplined systematic analysis of system failure modes. Moreover, to guarantee that the reconfiguration performed in response to the changed operating conditions achieves the required goals, fault tolerant systems should incorporate the appropriate monitoring and adaptation capabilities. Our third research question:

Research question 3. How can we facilitate systematic analysis of system failure modes, structure system architecture to support adaptability and verify fault tolerance capabilities?

aims at studying these problems.

In our thesis, we aim at finding potentially industry-relevant solutions addressing the identified research questions. Therefore, we will utilize the modeling and verification techniques that are used in the current industrial practice. Moreover, we will validate the proposed solutions in a number of case studies from different industrial domains.

**Organization of the Thesis.** This thesis consists of two parts. The overview of the research work reported in this thesis is included in Part I. Part II contains the original research publications.

Part I is organized as follows. Chapter 2 discusses the dependability concept and pays special attention to fault tolerance as one of the essential dependability attributes.

Chapter 3 overviews the development methodologies, which have been used in the thesis. In this section, we discuss UML, SystemC, SPIN model checker and the associated modeling language PROMELA. We illustrate a representation of different aspects of fault tolerance in the corresponding frameworks.

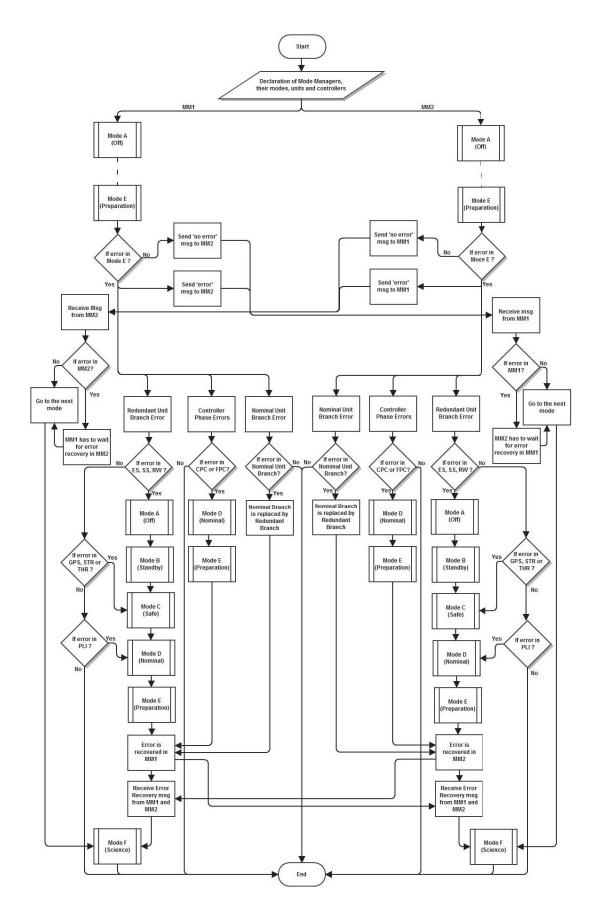

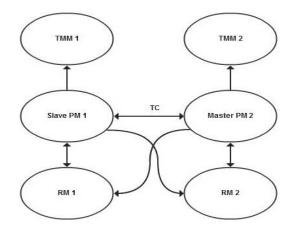

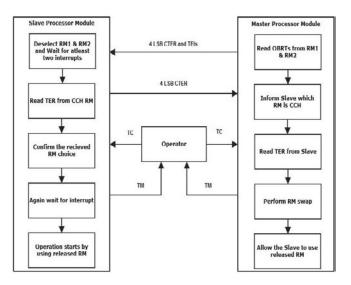

Chapter 4 focuses on the concept of modes and main issues in designing fault-tolerant mode-rich systems. We identify the problems and solutions in implementing distributed systems with the centralized as well as distributed mode management. We use a case study from the aerospace domain to illustrate the principles of achieving fault tolerance via mode transitions. In

particular, we demonstrate how to address the issue of ensuring correctness of mode logic. Moreover, we explain how to use the handshake protocol to synchronizing mode transitions in the distributed mode management.

Chapter 5 focuses on studying architectural aspects of fault tolerance. Firstly, we discuss how to modify and apply Failure Mode and Effect Analysis (FMEA) technique to systematically identify system failure modes and define architectural patterns for error masking or recovery. Then we outline the generic principles of architecting adaptable fault tolerant systems.

A detailed description of the published research papers is given in Chapter 6. The overview of the related work is presented in Chapter 7. Chapter 8 summarizes the main contributions of the research work carried out in this thesis, discusses its strengths and limitations, as well as outlines the future research directions.

## 2 Dependability and Fault Tolerance

In this chapter, we give an overview of the dependability concept and in particular, focus on the fault tolerance aspect.

### 2.1 Dependability Taxonomy

*Dependability* of a computing system is the ability to deliver service that can justifiably be trusted. The notion of dependability was introduced by Laprie [1] and further refined by Avizienis et al [2]. Nowadays complex computer-based systems are embedded in the infrastructures supporting the majority of critical services provided to our society. Therefore, dependability has become the concern of the highest priority in the development and operation of modern computer-based systems.

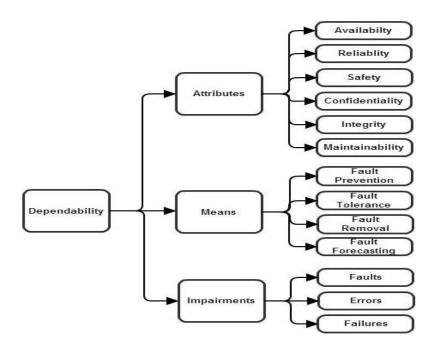

The variety of computing systems on whose services we need to place our reliance is broad - it ranges from satellite constellations, airplanes, nuclear power plants, or databases containing sensitive health records. Correspondingly, different characteristics of system behavior become the main priority in their development. For instance, for the satellite systems we need to guarantee a high degree of reliability, i.e., to ensure that despite an occurrence of faults and other environmental disturbances, the system can continuously operate for a certain period. For the airplanes and nuclear power plants, we should ensure that the system is safe, i.e., the likelihood of occurrence of hazardous failures is very low. Finally, for the databases containing sensitive data, we have to ensure a high degree of security, i.e., the absence of unauthorized access or data alternations. The concept of dependability provides us with a unified framework that allows us to address such diverse concerns within a single conceptual framework. It consists of three parts: dependability attributes, threats to dependability and means for achieving dependability. Figure 2.1 presents the dependability taxonomy [1].

The key attributes of dependability are given below:

- *Availability*: the ability of the system to provide a correct service at any given moment in time.

- *Reliability:* the ability of the system to provide a service under a given set of operating conditions over a specific time interval.

- *Safety:* the ability of the system to provide a service under the given conditions without jeopardizing its environment and users.

- *Maintainability:* the ability of the system to undergo repairs and modifications.

- *Integrity:* the ability of the system to prevent improper state alterations.

- *Confidentiality:* the absence of unauthorized disclosure of information.

The *threats* to dependability, often referred to as the impairments to dependability may introduce the unwanted alterations in the service provisioning. Dependability is impaired by the occurrence of faults, errors, and failures.

- *Fault*: a defect within the system. Faults can be generated due to internal factors (e.g., software coding mistakes, memory bit "stuck") and external factors (e.g., component defects or human mistakes). Faults may result in errors.

- *Error:* a deviation from the required operation of the system or subsystem. Errors are the effect of faults and may lead to subsequent system failure.

- *Failure:* a deviation in provisioning a required service to the system user. Failures are the effects of errors.

Figure 2.1: Dependability Taxonomy

The *means* for dependability are the techniques used to facilitate the development of dependable systems. The dependability means can be classified into four categories: fault prevention, fault removal, fault forecasting and fault tolerance.

- *Fault prevention:* the techniques aiming at reducing the likelihood of an introduction of faults during the process of system development.

- *Fault removal:* the techniques that facilitate identifying and removing the faults during the development stage as well as during the operational life of a system.

- *Fault forecasting:* the techniques that are applied to predict fault occurrence and evaluate their possible consequences on the system behavior.

- *Fault tolerance:* the techniques that ensure that the system can continue to deliver its services even in the presence of faults.

Since our thesis focuses on studying methods for achieving fault tolerance, below we give a detailed overview of the fault tolerance concept.

### 2.2 Fault Tolerance

The main aim of fault tolerance [3] is to ensure that the system continues to provide its services even in the presence of faults. Typically, fault occurrence leads to a certain service degradation. However, it is important to ensure that the system behaves in a predictable deterministic way even in the presence of faults.

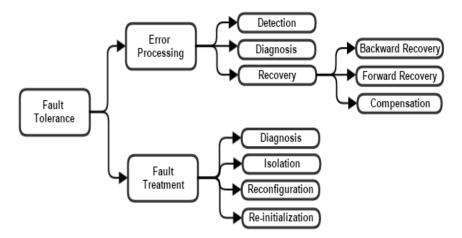

The main techniques to achieve fault tolerance are error processing and fault treatment, as shown in Figure 2.2.

Figure 2.2: Fault Tolerance Techniques

**Error processing:** Error processing comprises the measures applied while the system is operational. The purpose of error processing is to eliminate an error from the computational state and preclude failure occurrence. Error processing is usually implemented in three steps: error detection, error diagnosis, and error recovery [15].

- *Error detection:* determines the presence of error.

- *Error diagnosis:* evaluates the amount of damage caused by the detected error.

- *Error recovery:* aims at replacing an erroneous system state with the error-free state.

There are three types of error recovery methods: backward recovery, forward recovery and compensation.

- *Backward recovery:* tries to return the system to some previous error-free state. Typically, backward recovery is implemented by checkpointing, i.e., periodically, during the normal system operation, the state of the system is stored in the memory. In the case of a failure, the system retrieves the information about the error-free state from memory and resumes its functioning from this state.

- *Forward recovery:* upon detection of an error, the system makes a transition to a new error-free state from which it continues to operate. Exception handling is a typical example of forward error recovery.

- *Compensation:* can be used when the erroneous state contains enough redundancy to enable its transformation to an error-free state. Compensations are often used in complex transactions.

**Fault treatment:** aims at preventing faults from being activated again. Fault treatment is usually performed while the system is not operational, i.e., during the scheduled maintenance. Fault treatment comprises four steps: diagnosis, isolation, reconfiguration, and re-initialization.

- *Diagnosis* determines the causes of errors and focuses on localizing a fault and determining its nature.

- *Isolation* prevents faulty components from being used or activated in further system operations.

- *Reconfiguration* replaces the faulty components with the fault-free ones to provide an acceptable but possibly degraded service.

- *Re-initialization* is an update performed after the new configuration has taken place.

To implement fault tolerance, it is important to understand the types of faults that might occur in the system. Faults can be characterized as nature, duration or extent.

• *Nature:* We distinguish between random and systematic faults. The random faults are associated with hardware components. For the components that are the subjects of random faults, we can use the statistical analysis and estimate various characteristics, e.g., such as mean time between failures. Systematic faults are typically associated with the design errors, e.g., mistakes in the system specification or implementation. Since an error will occur each time the erroneous state is reached, statistical methods cannot be applied to the systematic faults. Systematic faults should be prevented by the use of fault avoidance and fault removal techniques.

- *Duration:* Faults can be classified regarding their duration into permanent, transient, and intermittent faults.

- Permanent faults: once they have occurred, they remain in the system during its entire operational life, if no corrective actions are performed.

- *Transient* faults can appear and then disappear after a short time.

- *Intermittent faults*: can appear, disappear and then reappear at a later time.

- *Extent:* Faults can be categorized according to their effect on the system as localized and global ones.

- *Localized* faults affect only a single hardware or software module.

- *Global* faults permeate throughout the system.

Hardware faults can be due to either random component failure or mistakes in the design. The faults can be permanent, transient, or intermittent and can have a global or local extent. Software faults are systematic. They occur due to mistakes in the design of the system. These faults can have an unlimited number of forms, e.g., coding faults, stack overflows or underflows, logical errors in calculations, use of uninitialized variables, etc.

To detect and recover from faults, we have to introduce some form of redundancy into the system design. *Redundancy* can be defined as the use of resources or components that would not have been needed if the systems were fault free. Next, we overview different forms of redundancy.

**Hardware redundancy** is defined as the use of additional hardware to detect or tolerate faults. Static, dynamic and hybrid redundancy are the three basic forms of hardware redundancy.

- *Static redundancy* allows the designers to implement fault masking, i.e., it allows the system to nullify the effect of fault occurrence.

- *Dynamic redundancy:* this form of redundancy allows the system to detect the faults and then perform reconfiguration to deactivate faulty components.

- *Hybrid redundancy:* This form of redundancy combines static and dynamic techniques. Fault masking is used to prevent the error propagation within the system, whereas fault detection and reconfiguration are used to remove faulty components from the system.

**Information redundancy**: The use of additional information that is required to implement a given function for the purpose of detecting or tolerating faults. The use of parity bits, checksums, and error detecting or correcting codes are the examples of this kind of redundancy.

**Temporal redundancy**: The use of additional time that is required to implement a given function for the purpose of detecting or tolerating faults. Temporal redundancy is used to tolerate transient faults, e.g., by repeating the failed computation.

**Software redundancy** can be defined as the use of additional software for the purpose of detecting or tolerating faults. Designing software that controls fault tolerance-related functionality is one of the main topics of our research work.

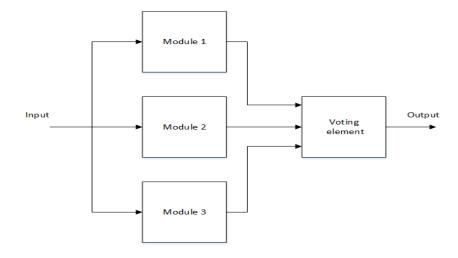

In this thesis, we consider static and dynamic forms of redundancy. The static redundancy relies on a voting mechanism that compares the outputs of some redundant modules and produces a majority view. This mechanism allows the system to mask an occurrence of faults. In practice, static redundancy is often implemented as the triple modular redundancy arrangement, as shown in

Figure **2.3**. The arrangement consists of three identical modules and one voting element. If the system is fault free, then each module produces the same output. Any difference between the outputs represents a failure in the module. A voting element nullifies the effect of any single failure by comparing the outputs and generating the output corresponding to the majority view. Therefore, the system can tolerate the failure of any single module.

Figure 2.3: Triple Modular Redundancy

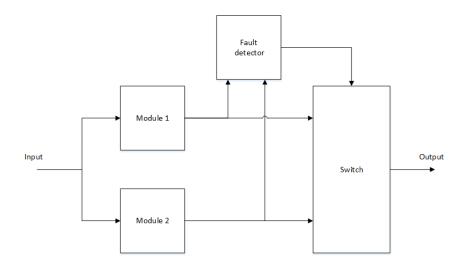

Dynamic forms of redundancy employ fault detection instead of fault masking approach. These systems attempt to detect faults and then to reconfigure to continue an error-free function. The effectiveness of the fault detection process determines the success of the dynamic redundancy. This approach minimizes the required number of redundant components because only two modules are required to cope with a single fault and three modules to cater for two faulty units. The examples of dynamic redundancy include a standby spare and a duplication pattern, as shown in

Figure **2.4** and Figure 2.5 respectively.

- **Standby spare:** In the standby spare arrangement, one module is in the operational state, while the other is in the standby state. A fault detection system is used to detect the faults and control the switch. In case the system is fault free, the switch generates the output corresponding to the output from the single operational module. When a fault is detected, the switch will reconfigure the system and generate the output corresponding to the output produced by the standby module.

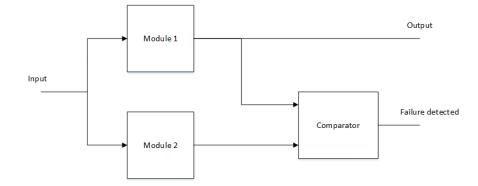

- **Duplication pattern:** In the duplication pattern, the same input signal is fed into two identical modules. The comparator compares the outputs from both modules and generates a failure detection signal in case a discrepancy is detected. One of the module's output is then passed to the next stage.

Figure 2.4: Dynamic redundancy: standby spare

Figure 2.5: Dynamic redundancy: duplication pattern

In modern computer-based systems, fault tolerance is often implemented by software. The software is responsible for detecting faults, initiating error recovery and performing reconfiguration. To design software, which is responsible for implementing fault tolerance, we should analyze some factors including the nature of faults, possibility to introduce hardware redundancy in the system design, timing and memory constraints, and availability of information and timing redundancy, etc. Therefore, the basic concepts that we have described above constitute an important background for designing fault-tolerant systems. However, redundancy and corresponding functionality required to control it inevitably introduce additional complexity into the system design. Since complexity is commonly perceived as one of the main dependability threat, we should employ a disciplined software development process and formal reasoning to ensure functional correctness of fault-tolerant software-intensive systems.

In the next chapter, we overview the methodologies that we used in our thesis to design software that is responsible for fault tolerance assurance.

## 3 Design and Verification Methods

To cope with the complexity of modern software-intensive systems, we should rely on structured and rigorous approaches for software development. Such approaches allow us to build robust system architectures and ensure functional correctness of system behavior.

The range of modeling techniques is broad and spans from graphical notations to formal mathematical languages. Visual modeling frameworks are widely used in industry. However, in the safety-critical domain, formal approaches are also used to verify critical system functions. Since, in our thesis, we aim at proposing a practice-oriented approach to development and verification of fault-tolerant systems, in our work we adopt both graphical and formal modeling techniques. Next, we overview them and present various examples of modeling fault tolerant aspects.

#### 3.1 UML

Unified Modelling Language (UML) [16, 19] is a framework for visualizing and documenting software systems. It has become de-facto industry standard graphical notation for describing software analysis and designs. UML employs object-oriented style and is independent of a specific programming language [23].

UML supports model-driven software development. It is a part in a variety of applications including complex distributed systems. The language employs a set of specific symbols to graphically represent various components and relationships between them [16, 19]. There are several automated environments that support modeling in UML. Some of them also offer a possibility to generate the program code from the defined graphical models.

The most useful UML diagrams are use case diagram, class diagram, sequence diagram, state diagram, activity diagram and component diagram. In our thesis, we mainly used a subset of them that comprises use case diagram, class diagram, state diagram and sequence diagram. We describe them next.

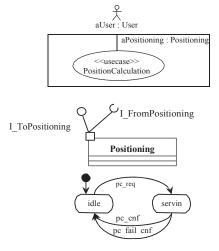

A *use case* represents a unit of functionality provided by the system [9]. The main goal of the use-case diagram is to support the development teams in visualizing the functional requirements of a system and defining the relationships with actors – the human users or other subsystems interacting with the modeled system. An example of a use case diagram is shown in

Figure **3.1**.

Figure 3.1: Example of a Use Case Diagram

The diagram shows two actors *User1* and *User2* that interact with the system while it provides a functionality called *Service*. Often the use case diagram represents the essential system processes and relationships among different use cases. Typically, a use-case diagram shows a group of use cases — either all use cases of the system under construction or a particular subset of use cases with related functionality.

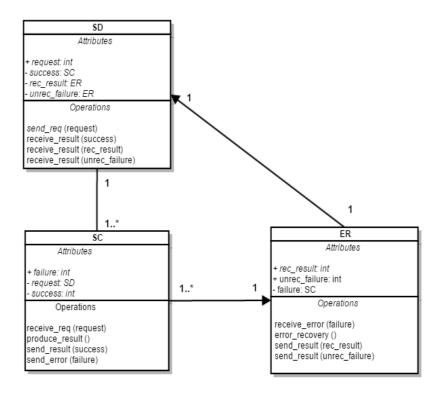

The *class diagram* [11] shows how system entities relate to each other, i.e. it defines the static structure of the system [9]. The class diagrams are usually used to display the classes about the real-world purpose of the system, so called logical classes. The class diagrams also depict the relationships between the classes, such as inheritance or association.

In our work, we aim at making the fault tolerance aspect explicit during system modeling, design, and verification. Hence, we propose a number of generic patterns that allow the designers to represent system behavior not only in the nominal conditions but also in the presence of faults.

An example of a class diagram with an explicit representation of fault tolerance aspect is given in Figure 3.2. The diagram shows three classes called SD, SC, and ER. The classes are defined to explicitly represent the steps of fault tolerance-aware service architecture. The class SD is responsible for the communication with the user. Moreover, it orchestrates the work of the service executing component SC and error handler ER. SC implements the main functionality of the service. Since service execution might fail or succeed, the SC class contains attributes *failure* and *success*. The ER class implements error recovery functionality that again might succeed or fail, as designated by the corresponding attributes *rec\_result* and *unrec\_failure*. The dynamics of the class interactions is explained in the accompanying sequence diagram.

Figure 3.2: Example of a Class Diagram

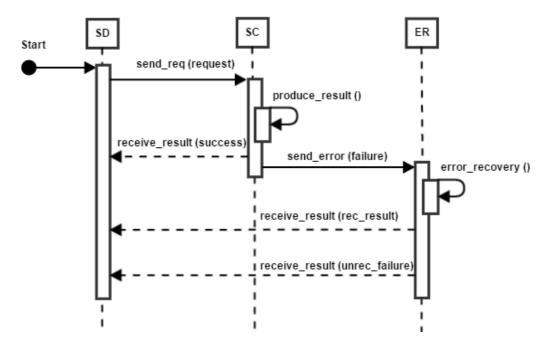

A sequence diagram [10] shows a detailed flow of control that is typically defined for a specific use case (*Service* in our case). The sequence diagrams show the calls between the objects in a sequence. A sequence diagram has two dimensions – the vertical and horizontal. The vertical dimension shows the sequence of messages/calls in the time order that they occur. The horizontal dimension shows the object instances to which the messages are sent.

The top of the diagram contains the identities of the class instances (objects). To show that a class instance sends a message to another class instance, we draw a line with an open arrowhead pointing to the receiving class instance and place the name of the message/method above the line. The returned message is drawn with a dotted line with an arrowhead pointing back to the originating class instance. It is labeled with the return value above the dotted line.

An example of a sequence diagram is given in Figure 3.3. Here we again demonstrate how to explicitly introduce handling of faulty behavior into the service design. We define three processes – Service Director (SD), Service Component (SC) and Error Recovery (ER) as the corresponding parallel vertical lines. The interactions between the processes are carried out according to the communication between the service and its user in a time sequence.

SD plays two roles: it handles the user communication with the service and controls the service execution flow. The user sends a request to execute a service. The request is received by the service director SD. SD initiates service execution by sending a message *send\_req(request)* to SC. SC tries to execute the requested service. In case it completes its execution, it returns the message *success* to the service director. In case it fails, it sends a *failure* message to ER, i.e., requests to initiate error recovery. ER notifies SD about success *rec\_result* or failure *unrec\_failure* of error recovery.

Figure 3.3: Example of a Sequence Diagram

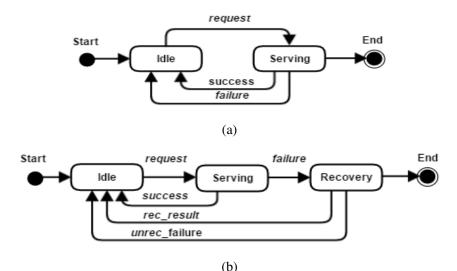

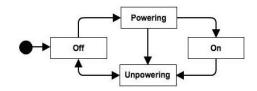

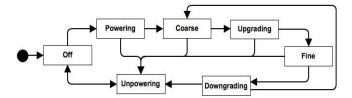

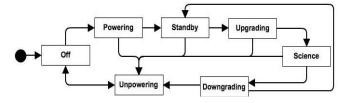

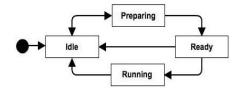

Another diagram representing the dynamic system behavior is the state diagram. The *state diagrams* represent the different states that a class or the entire system can be in and define the transitions from state to state. The state diagram has five basic elements: the initial starting point (a solid circle), a transition between states (a line with an open arrowhead), a state (a rectangle with rounded corners), a decision point (an open circle) and one or several termination points (a circle with a solid circle inside it).

An example of a state diagram defined on a system level is shown in Figure 3.4. The model depicts the communication between the service and its user. To request the service execution, the user generates an event *request* that is received by the service. The request is always replied either with *success* in the case of error-free system or *failure* in the case of error occurrence during the service provisioning.

In Figure 3.4 (a), the possibility of failed response is represented explicitly. This corresponds to the error detection step of fault tolerance implementation. The next extension would be to explicitly define the error recovery stage, as shown in Figure 3.4 (b). If the system is fault-free, then the service execution terminates normally and produces the required results together with the notification of success. If an error occurs, the system makes a transition to the recovery state. If the error recovery is successful, the system continues to operate normally; otherwise the *unrec\_failure* event is generated designating that an unrecoverable error has occurred in the system.

Figure 3.4: Examples of State Diagram (a) with explicit representation of failure (b) with explicit representation of failure and error recovery

UML helps to analyze, visualize and discuss the design of software systems with different stakeholders. It is widely accepted in the industry due to its readability. However, as a graphical notation, it lacks formality. Nevertheless, it is a useful front end for a more rigorous notation, such as SystemC that we discuss next.

## 3.2 SystemC

SystemC [12, 13] is a widely used system-level modeling language [14] that allows the designers to represent the system design at different abstraction levels as well as use various design methodologies. The SystemC specifications can contain a mixture of abstract models and implementation-level code. The specifications are executable. Moreover, the framework supports simulation that allows exploring not only functional but also architectural alternatives.

SystemC provides us with a unified language to define both hardware and software components. SystemC-based design platforms help to cope with the complexity of system-level design and often result in reducing system development cost and time. SystemC has become de-facto verification standard in real-time embedded systems such as MARTE [17]. It is extensively used in industrial sectors such as electronic systems, semiconductor technologies, electronic design automation and embedded software.

SystemC is a high-level, powerful design language written in standard C++. SystemC uses C++ Class libraries and C/C++ Compiler (such as bcc, gcc, etc.). It introduces timing, concurrency and structure-related constructs to model system architecture. It provides capabilities similar to VHDL (Very-High-Speed Integrated Circuit Hardware Description Language) and strong simulation kernel that also supports hardware/software co-simulation.

The language of SystemC includes the following constructions: modules, ports, data types, processes, channels, interfaces, and events.

*Modules* are the basic building blocks of the language. They allow a designer to partition system design into smaller parts that encapsulate internal data representation and algorithms from the rest of the system. Hence, a SystemC model usually consists of several modules.

A typical module contains *ports* via which the modules communicate with each other, processes describing the functionality of a module, internal data, and channels representing model state and communication between processes.

A template for representing a module in SystemC is given in Figure 3.5.

```

SC_MODULE(Name) {

// ports, processes, internal data, etc

SC_CTOR (Name) {

// body of construction:

//process declaration, event sensitivities etc.

}

};

```

Figure 3.5: Definition of simple SystemC module

The SC\_MODULE macro designates that the class Name is derived from the library class sc\_module. The macro SC\_CTOR declares a constructor, which maps the membership functions to processes and declares event sensitivities. The argument should be the name of the module that is currently declared.

Modules can be instantiated, i.e., there might be several instances with the identical structure and functionality that are described by one common module definition.

SystemC uses interfaces, ports, and channels to provide the abstract modeling primitives for representing communication between modules. *Channels* are used to model the actual data transmission; *interfaces* describe the sets of operations that the channel provides. Finally, *ports* are the proxy objects that facilitate access to the channels through the interfaces. Often one can say that the port is bound to the channel through an interface.

An interface consists of a set of *operations*. For each operation, it specifies the operation's name, parameters and returns value. The abstract base class sc\_interface is used to derive interfaces in SystemC. It also provides a virtual function register\_port(), which is called to connect a channel with the port via the interface.

Let us consider an example of a simple interfaces sc\_signal\_in\_if<S>. It is derived from sc\_interface and parametrised by the datatype S. As such, it provides a virtual function read() that returns constant reference to S. Similarly, the interface sc\_signal\_inout\_if<S> provides a virtual function write() that takes as parameter a constant reference to S. Since sc\_signal\_inout\_if<S> is derived from sc\_signal\_in\_if<S>, it also inherits the function read(). The semantics of these functions is to read from and write to the channel that implements the corresponding interface.

Interfaces significantly improve reusability of the modules that we create. The next step is supporting reusability to provide modules with the ports that allow them to connect and communicate with the rest of the system.

Ports correspond to interfaces and represent the objects derived from an abstract class sc\_port\_base. Figure 3.6 shows a template class for creating ports.

Figure 3.6: SystemC template for creating ports

The template class sc\_port has two parameters: an interface IF through which the ports may be connected and an optional integer N denoting the maximum number of interfaces that may be attached to the defined port. The method of the port is operator  $\rightarrow$ (). It returns a pointer to the interface with which the port is associated.

For instance, we can map the following declaration of the port p into the definition of the module SC\_MODULE given in Figure 3.5:

#### sc\_port<sc\_signal\_inout\_if<int> > p

The port accesses a channel [18] through the interface sc\_signal\_inout\_if<int>. Since the interface provides the read() and write() methods, we can read the value of the channel and write to it using the expressions p->read() and p->write().

*Process* is a basic unit of functionality that is comprised of a module. Processes provide us with the means to simulate concurrent behavior, since in embedded fault-tolerant systems many activities are run in parallel.

A process is a member function of a module and is defined in the module construction. A defined process accesses external channels through the ports of its containing module. There are two kinds of processes: method process declared with the macros SC\_METHOD and thread process declared correspondingly as SC\_THREAD.

Figure 3.7 shows an example of a module with a method process declaration.

```

SC_MODULE(Maximum) {

sc_in<int> n1;

sc_in<int> n2;

sc_out<in> max_n1_n2;

void find_max() {

if (n1>n2) then max_n1_n2 = n1

else max_n1_n2 = n2;

}

SC_CTOR (Maximum) {

SC_METHOD (find_max);

sensitive << n1 <<n2;

}

};</pre>

```

Figure 3.7: Example of a module with a method process declaration

When the membership function find\_max is invoked, it calculates the maximum of the inputs n1 and n2 and writes the result to the output  $\max_{n1_n2}$ . However, the member function does not create a process as such. The process is created inside the constructor by the statement SC\_METHOD(Maximum), which maps the member function to a method process by registering it with the scheduler. The next statement defines that this process is sensitive to changes in the values of signals that will be connected to the input ports, i.e., when n1 and n2 change, the value of  $\max_{n1_n2}$  is recalculated.

Next, we show how to describe the proposed architectural and behavioural the pattern for fault tolerance-explicit service design described in Chapter 3-1 in SystemC. The fragment of the code in Figure 3.8 illustrates that as a reaction to a service request received from a user, the service director sends a request to the service component. The service component can either succeed or fail to execute a service, i.e., it produces outputs *success* or *failure*.

The *class1* module can only call member functions of SD interface. Similarly, the *class2* module can only call member functions of SC interface. The process describes the functionality of the SD and SC in each respective module blocks. The SC receives a command from SD according to user's request (i.e., *request*). SC class generates output (i.e., *result* in the case of success, or *failure* in case of error). In the case of failure, error recovery is carried out, i.e., ER class produces *rec\_result* in the case of recoverable error and *unrec\_failure* otherwise. In the absence of faults, the service returns *success*.

class SD: public sc\_interface { // SD class public: int request; }; class SC: public sc\_interface { // SC class public: int result = 1; int failure = 0; int out\_; void output(const SD &sd){ if (sd.request == 1) out\_ = result; // error-free else // fault out\_ = failure; }; class ER: public sc\_interface { // ER class public: int failure = 0; int rec\_result = 1; int unrec\_failure = 0; int out\_; void error(const SC &sc){ if (sc.out == failure) out\_ = rec\_result; // recovered fault else // unrecoverable fault out\_ = unrec\_failure; }; SC\_MODULE(class1) { // module declaration public: sc\_port<SD> req; // port SC\_CTOR(class1) { // constructor SC\_THREAD(main); } void main(){ // process req.request = 1;}; SC\_MODULE(class2) { // module declaration public: sc\_port<SC> out; // port // constructor SC\_CTOR(class2) { SC\_THREAD(main);} void main(){ // process out.output();}};

| SC_MODULE(class3) {                                             | // module declaration       |  |

|-----------------------------------------------------------------|-----------------------------|--|

| public:                                                         |                             |  |

| sc_port <er> out;</er>                                          | // port                     |  |

| SC_CTOR(class3) {                                               | // constructor              |  |

| SC_THREAD(main);}                                               |                             |  |

| <pre>void main(){</pre>                                         | // process                  |  |

| out.error();} };                                                |                             |  |

| SC_MODULE(top) {                                                | // top level serving module |  |

| public:                                                         |                             |  |

| SC S_C; SD S_D; ER E_R;                                         |                             |  |

| class1* service_director; class2* service_component;            |                             |  |

| class3* error_recovery;                                         |                             |  |

| SC_CTOR(top) {                                                  | // constructor              |  |

| <pre>service_director = new class1("Service_Director");</pre>   |                             |  |

| <pre>service_director -&gt; req(S_C);</pre>                     |                             |  |

| <pre>service_component = new class2("Service_Component");</pre> |                             |  |

| <pre>service_component -&gt; out(S_D);</pre>                    |                             |  |

| error_recovery = new class3("Error_Recovery");                  |                             |  |

| error_recovery -> out(E_R);};                                   |                             |  |

Figure 3.8: SystemC Implementation of Fault Tolerant Service Pattern

SystemC provides us with a systematic framework for modeling complex fault tolerant systems. However, as we have discussed previously, fault tolerance introduces additional complexity in the system design and hence increases the likelihood of design mistakes. To ensure correctness of fault tolerance mechanisms, we should employ the techniques used for fault avoidance, i.e., use formal verification. The most widely formal verification technique is model checking. Next, we describe it in details and present an example of properties that should be verified to guarantee the correctness of fault tolerant systems.

## **3.3 Model Checking Fault-Tolerant Systems**

### 3.3.1 Model Checking: Introductory Background

Model checking is a verification technique for verifying functional properties of computing systems [98, 99, 100, 101,102]. Model checking takes as an input a finite-state model of the system and the desired property and systematically checks whether the given model satisfies this property. Typically, the properties that we are interested in checking include deadlock freedom, invariants, and request- response properties.

Model checking is an automated technique that allows us to check the absence of errors (i.e., property violations) in the system, i.e., to establish that the system under consideration has certain properties. In the majority of distributed systems including fault tolerant systems, we would at least be interested in establishing that a system never reaches a situation in which no progress can be made. In other words, more often than not, we are interested at least in verifying that no deadlock scenario can be found in the specification of the system.

Since the system specification defines the behavior of the system under consideration, the specification constitutes the basis for any verification activity. The system is correct only if it satisfies all properties derived from its specification. Once a state is found that does not satisfy one (or several) of the specification's properties, we can claim that we have discovered an error in the design. Therefore, correctness as such is relative to a specification.

Model checking is a verification technique that explores all possible system states in a brute-force manner. State-of-the-art model checkers can handle state spaces containing up to  $10^9$  states. The use of optimizing algorithms and abridged data structures sometimes allows the model checkers to tackle models containing up to  $10^{20}$  states.

The system model is usually automatically generated from a model given in some programming language like C or modeling language like SystemC or Promela (which we present later). The model checker examines all system states to check whether they satisfy a particular property. If the model checker encounters a state that violates the property under consideration, it generates a counterexample indicating how the undesired state can be reached. Essentially, the counterexample shows an execution path leading from the initial system state to a state that violates the verified property.

A standard way to represent a model is by a transition system – a directed graph where nodes represent states and edges model transitions, i.e., state changes. A state represents some information about a system at a certain moment of its behavior. Formally, a transition system *TS* is defined as a tuple  $(S,Act, \rightarrow, I,AP,L)$  where

- *S* is a set of states,

- *Act* is a set of actions,

- $\rightarrow \subseteq S \times Act \times S$  is a transition relation,

- $I \subseteq S$  is a set of initial states,

- *AP* is a set of atomic propositions, and

- $L: S \rightarrow 2^{AP}$  is a labeling function.

*TS* is called finite if *S*, *Act* and *AP* are all finite. In our definition, we describe the transition systems with the action names for the transitions (state changes) and the atomic propositions for the states. Intuitively, the behavior of a transition system is as follows: the system starts in some initial state  $s_0 \in I$  and evolves according to the transition relation  $\rightarrow$ , i.e., if *s* is the current state, then a transition  $s \rightarrow \alpha s'$  originating from *s* is selected non-deterministically and taken. This means that the action  $\alpha$  is performed and *TS* evolves from state *s* into the state *s'*. The procedure repeats until a state that does not have outgoing transitions is reached.

The labeling function L relates a set  $L(s) \in 2^{AP}$  of atomic propositions to any state s, i.e., L(s) identifies only those atomic propositions  $a \in AP$ , which are satisfied by state s. For a given propositional logic formula  $\Phi$ , s satisfies the formula  $\Phi$  if the evaluation induced by L(s) makes the formula  $\Phi$  true, i.e.,

### $s \models \Phi$ iff $L(s) \models \Phi$

Let us consider a simple example – a road crossing. We have two traffic lights regulating the car movement in the orthogonal direction. Both traffic lights have two states: red and green. Both traffic lights are described by the similar transition systems consisting of two states: red and green and two transitions: a and b indicating the change of the light. For the first traffic light  $red \rightarrow {}^a$  green and green  $\rightarrow {}^b$  red. For the second traffic light  $red \rightarrow {}^b$  green and green  $\rightarrow {}^a$  red correspondingly. The crossing can be represented as a parallel composition of two transition systems. Both traffic lights synchronize using the actions a and b indicating the change of the light. Let us assume that the initial state for both of them is red. Since the first traffic light is waiting to be synchronized with action b. It represents deadlock and an obvious mistake in the system design.

Linear Temporal Logic (LTL) provides an intuitive but mathematically rigorous notation for expressing properties about state labels in the model execution. LTL formulae over the set AP of atomic propositions are formulated using the following grammar:

$$\varphi ::= true \mid a \mid \varphi_1 \land \varphi_2 \mid \neg \varphi \mid O \varphi \mid \varphi_1 \cup \varphi_2$$

where  $a \in AP$ .

The until operator allows us to derive temporal modalities  $\diamond$  eventually, "sometimes in the future" and  $\Box$  always, "from now on forever" as follows:

$$\Diamond \phi = \text{true } \cup \phi \text{ and } \Box \phi = \neg \Diamond \neg \phi$$

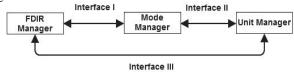

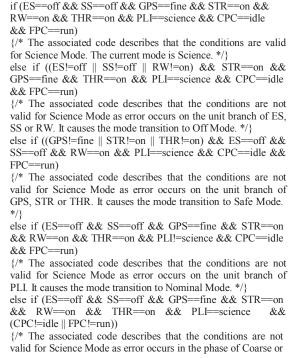

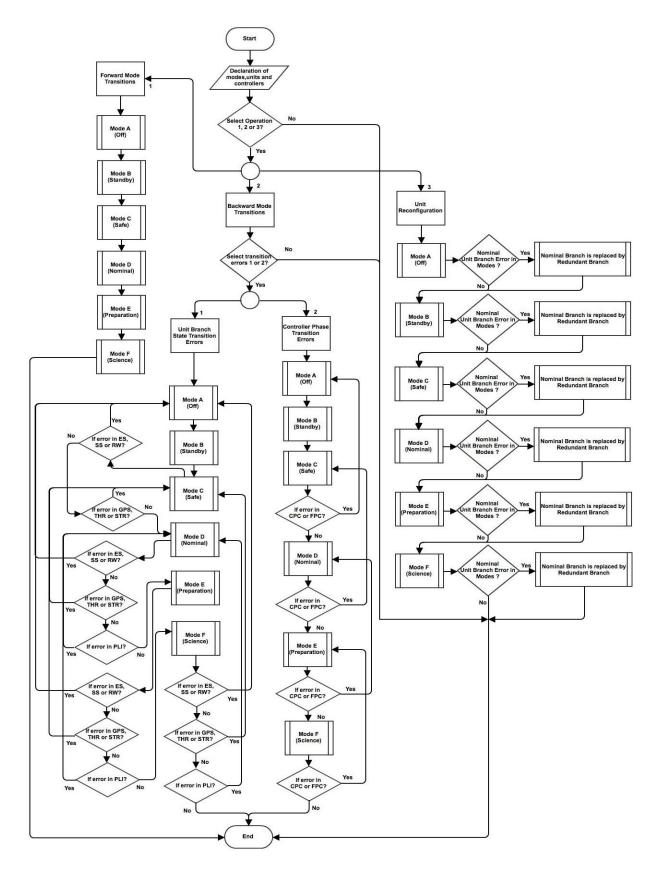

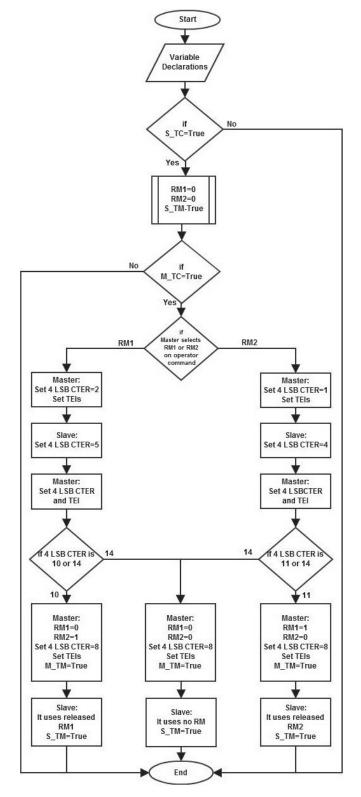

For instance, let us express the property that two processes P1 and P2 never simultaneously access their critical section (a shared resource):